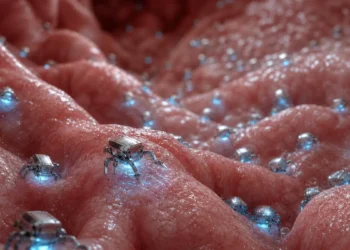

Dans la course effrénée à la miniaturisation des composants électroniques, une équipe de chercheurs de Penn State (USA) semble avoir trouvé une voie prometteuse pour repousser les frontières actuelles. Leur proposition ? L’intégration 3D de matériaux 2D, une innovation qui pourrait bien bouleverser les règles du jeu dans l’industrie des semi-conducteurs

La loi de Moore à l’épreuve du temps

La loi de Moore, un principe fondamental pour les dispositifs électroniques, prévoit que le nombre de transistors sur une puce doublera tous les deux ans, garantissant ainsi une puissance de calcul accrue. Une limite existe toutefois. Les puces les plus avancées d’aujourd’hui abritent près de 50 milliards de transistors dans un espace pas plus grand que votre ongle.

Selon les chercheurs de Penn State, la tâche de compresser encore plus de transistors dans cette zone confinée devient de plus en plus difficile.

L’intégration 3D avec des matériaux 2D : une solution prometteuse

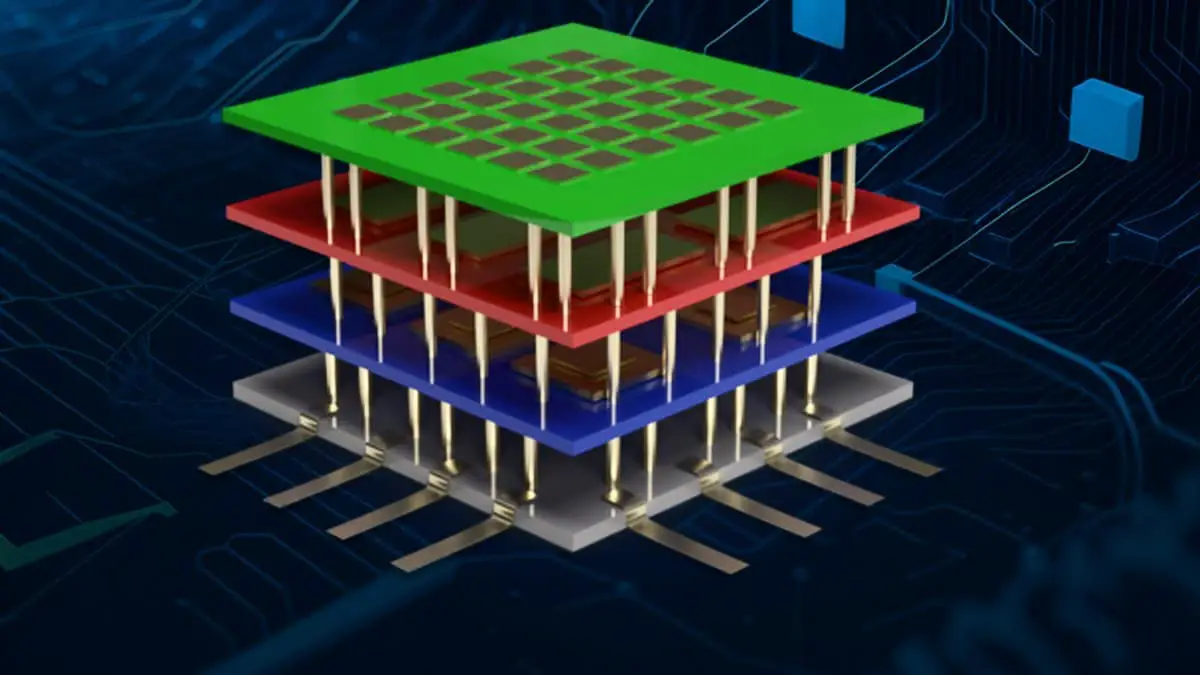

Dans une étude publiée dans la revue Nature, Saptarshi Das, professeur associé de science et de mécanique de l’ingénierie et co-auteur correspondant de l’étude, et son équipe suggèrent un remède : mettre en œuvre sans heurt l’intégration 3D avec des matériaux 2D.

Dans le monde des semi-conducteurs, l’intégration 3D signifie empiler verticalement plusieurs couches de dispositifs semi-conducteurs. Cette approche non seulement facilite l’intégration de plus de transistors à base de silicium sur une puce informatique, communément appelée «More Moore», mais permet également l’utilisation de transistors fabriqués à partir de matériaux 2D pour incorporer diverses fonctionnalités au sein des différentes couches de la pile, un concept connu sous le nom de « More than Moore« .

Défis et avantages de l’intégration 3D monolithique

L’intégration 3D monolithique présente des défis significatifs, selon Darsith Jayachandran, assistant de recherche diplômé en science et mécanique de l’ingénierie et co-auteur correspondant de l’étude, car les composants en silicium conventionnels fondraient sous les températures de traitement.

Par contre l’intégration 3D avec des dispositifs 2D présente plusieurs autres avantages, selon les chercheurs. L’un d’eux est une mobilité de porteur supérieure, qui se réfère à la manière dont une charge électrique est transportée dans les matériaux semi-conducteurs. Un autre est d’être ultra-mince, permettant aux chercheurs de placer plus de transistors sur chaque niveau de l’intégration 3D et d’activer plus de puissance de calcul.

En synthèse

Alors que la plupart des recherches universitaires impliquent des prototypes à petite échelle, cette étude a démontré l’intégration 3D à une échelle massive, caractérisant des dizaines de milliers de dispositifs.

Selon Saptarshi Das, cette réalisation comble le fossé entre le monde universitaire et l’industrie et pourrait conduire à de futurs partenariats où l’industrie exploite l’expertise et les installations de Penn State en matière de matériaux 2D.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Pour une meilleure compréhension

Qu’est-ce que l’intégration 3D avec des matériaux 2D ?

C’est une technique qui consiste à empiler verticalement plusieurs couches de dispositifs semi-conducteurs, en utilisant des matériaux 2D pour incorporer diverses fonctionnalités au sein des différentes couches de la pile.

Quels sont les avantages de cette technique ?

Elle permet d’augmenter la densité de transistors sur une puce, d’ajouter de nouvelles fonctionnalités aux dispositifs électroniques et de réduire la consommation d’énergie.

Quels sont les défis de cette technique ?

Les défis incluent la gestion des températures de traitement élevées qui pourraient endommager les composants en silicium conventionnels.

Qu’est-ce que cela signifie pour l’industrie des semi-conducteurs ?

Cela pourrait ouvrir la voie à de nouvelles collaborations entre le monde universitaire et l’industrie, avec l’industrie exploitant l’expertise et les installations de Penn State en matière de matériaux 2D.

Qu’est-ce que cela signifie pour la loi de Moore ?

Cela pourrait permettre de dépasser les limites actuelles de la loi de Moore en augmentant le nombre de transistors sur une puce au-delà de ce qui est actuellement possible.

Références

Illustration : Des chercheurs de l’État de Pennsylvanie ont démontré l’intégration 3D de semi-conducteurs à grande échelle, en caractérisant des dizaines de milliers de dispositifs utilisant des transistors 2D fabriqués avec des semi-conducteurs 2D, ce qui permettra peut-être aux gadgets électroniques de devenir plus intelligents et plus polyvalents. Crédit : Elizabeth Flores-Gomez Murray/Institut de recherche sur les matériaux. Tous droits réservés.

Article : « Three-dimensional integration of two-dimensional field-effect transistors » – DOI: https://www.nature.com/articles/s41586-023-06860-5