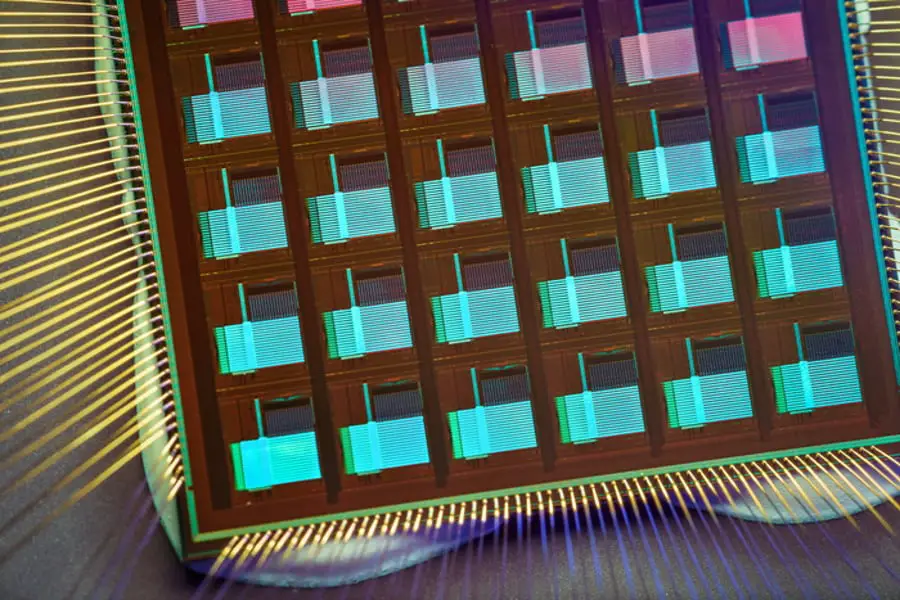

Une équipe internationale de chercheurs a conçu et fabriqué une puce qui exécute des calculs directement en mémoire et peut faire fonctionner une grande variété d’applications d’IA – le tout à une fraction de l’énergie consommée par les plateformes informatiques pour l’IA à usage général.

La puce neuromorphique NeuRRAM rapproche l’IA d’un fonctionnement sur une large gamme d’appareils périphériques, déconnectés du nuage, où ils peuvent exécuter des tâches cognitives sophistiquées partout et à tout moment sans dépendre d’une connexion réseau à un serveur centralisé. Les applications abondent aux quatre coins du monde et dans toutes les facettes de notre vie, qu’il s’agisse de montres intelligentes, de casques VR, d’oreillettes intelligentes, de capteurs intelligents dans les usines ou de rovers pour l’exploration spatiale.

La puce NeuRRAM est non seulement deux fois plus économe en énergie que les puces « compute-in-memory » de pointe, une catégorie innovante de puces hybrides qui exécutent des calculs en mémoire, mais elle fournit également des résultats tout aussi précis que les puces numériques classiques. Les plateformes d’IA conventionnelles sont beaucoup plus volumineuses et sont généralement contraintes d’utiliser de grands serveurs de données fonctionnant dans le nuage.

En outre, la puce NeuRRAM est très polyvalente et prend en charge de nombreux modèles et architectures de réseaux neuronaux différents. Par conséquent, la puce peut être utilisée pour de nombreuses applications différentes, notamment la reconnaissance et la reconstruction d’images ainsi que la reconnaissance vocale.

« Or, notre puce NeuRRAM est efficace sans sacrifier la polyvalence« , a déclaré Weier Wan, premier auteur correspondant de l’article et récent titulaire d’un doctorat de l’université de Stanford, qui a travaillé sur la puce à l’université de San Diego, où il était conseillé par Gert Cauwenberghs du département de bio-ingénierie.

L’équipe de recherche, codirigée par des bioingénieurs de l’université de Californie à San Diego, présente ses résultats dans le numéro de Nature du 17 août.

Actuellement, l’IA est à la fois gourmande en énergie et coûteuse en calculs. La plupart des applications d’IA sur les appareils périphériques impliquent le transfert de données des appareils vers le nuage, où l’IA les traite et les analyse. Les résultats sont ensuite renvoyés vers l’appareil. Cela s’explique par le fait que la plupart des périphériques sont alimentés par des batteries et ne disposent donc que d’une quantité limitée d’énergie pouvant être consacrée au calcul.

En réduisant la consommation d’énergie nécessaire à l’inférence de l’IA à la périphérie, cette puce NeuRRAM pourrait conduire à des dispositifs périphériques plus robustes, plus intelligents et plus accessibles, ainsi qu’à une fabrication plus intelligente. Elle pourrait également conduire à une meilleure confidentialité des données, car le transfert de données des appareils vers le cloud s’accompagne de risques de sécurité accrus.

Sur les puces d’IA, le déplacement des données de la mémoire vers les unités de calcul constitue un goulot d’étranglement majeur.

« Cela équivaut à faire un trajet de huit heures pour une journée de travail de deux heures« , a déclaré Wan.

Pour résoudre ce problème de transfert de données, les chercheurs ont utilisé ce que l’on appelle la mémoire vive résistive, un type de mémoire non volatile qui permet de calculer directement dans la mémoire plutôt que dans des unités de calcul séparées. La RRAM et d’autres technologies de mémoire émergentes utilisées comme réseaux de synapses pour l’informatique neuromorphique ont été mises au point dans le laboratoire de Philip Wong, conseiller de Wan à Stanford et principal contributeur à ces travaux. Le calcul avec des puces RRAM n’est pas nécessairement nouveau, mais il entraîne généralement une diminution de la précision des calculs effectués sur la puce et un manque de flexibilité dans l’architecture de la puce.

« Le calcul en mémoire est une pratique courante dans l’ingénierie neuromorphique depuis son introduction il y a plus de 30 ans« , a déclaré Cauwenberghs. « Ce qui est nouveau avec la NeuRRAM, c’est que l’efficacité extrême va désormais de pair avec une grande flexibilité pour diverses applications d’IA, sans pratiquement aucune perte de précision par rapport aux plates-formes de calcul numériques polyvalentes standard.«

Une méthodologie soigneusement élaborée a été la clé de ce travail, avec de multiples niveaux de « co-optimisation » à travers les couches d’abstraction du matériel et du logiciel, de la conception de la puce à sa configuration pour exécuter diverses tâches d’IA. En outre, l’équipe a veillé à tenir compte de diverses contraintes allant de la physique des dispositifs de mémoire aux circuits et à l’architecture des réseaux.

« Cette puce nous fournit désormais une plateforme permettant de résoudre ces problèmes à tous les niveaux, depuis les dispositifs et les circuits jusqu’aux algorithmes« , a déclaré Siddharth Joshi, professeur adjoint d’informatique et d’ingénierie à l’université de Notre Dame, qui a commencé à travailler sur le projet en tant qu’étudiant en doctorat et chercheur postdoctoral dans le laboratoire de Cauwenbergh à l’université de San Diego.

Performances de la puce

Les chercheurs ont mesuré l’efficacité énergétique de la puce par une mesure connue sous le nom de produit énergie-retard, ou EDP. L’EDP combine à la fois la quantité d’énergie consommée pour chaque opération et le temps qu’il faut pour réaliser l’opération. Selon cette mesure, la puce NeuRRAM atteint un EDP de 1,6 à 2,3 fois inférieur (plus il est faible, mieux c’est) et une densité de calcul de 7 à 13 fois supérieure à celle des puces les plus récentes.

Les chercheurs ont exécuté diverses tâches d’intelligence artificielle sur la puce. Elle a atteint une précision de 99 % dans une tâche de reconnaissance de chiffres manuscrits, de 85,7 % dans une tâche de classification d’images et de 84,7 % dans une tâche de reconnaissance de commandes vocales Google. En outre, la puce a également permis de réduire de 70 % l’erreur de reconstruction d’image dans une tâche de récupération d’image. Ces résultats sont comparables à ceux des puces numériques existantes qui effectuent des calculs avec la même précision binaire, mais avec des économies d’énergie considérables.

Les chercheurs soulignent que l’une des principales contributions de cet article est que tous les résultats présentés sont obtenus directement sur le matériel. Dans de nombreux travaux antérieurs sur les puces de calcul en mémoire, les résultats des repères d’IA étaient souvent obtenus en partie par simulation logicielle.

Les prochaines étapes consistent à améliorer les architectures et les circuits et à adapter la conception à des nœuds technologiques plus avancés. Les chercheurs prévoient également de s’attaquer à d’autres applications, telles que les réseaux de neurones à pointes.

« Nous pouvons faire mieux au niveau des dispositifs, améliorer la conception des circuits pour mettre en œuvre des fonctionnalités supplémentaires et aborder diverses applications avec notre plateforme NeuRRAM dynamique« , a déclaré Rajkumar Kubendran, professeur adjoint à l’université de Pittsburgh, qui a commencé à travailler sur le projet alors qu’il était étudiant en doctorat dans le groupe de recherche de Cauwenberghs à l’UC San Diego.

En outre, Wan est membre fondateur d’une startup qui travaille à la production de la technologie de calcul en mémoire. « En tant que chercheur et ingénieur, mon ambition est de mettre en pratique les innovations issues des laboratoires« , a déclaré M. Wan.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Nouvelle architecture

La clé de l’efficacité énergétique de la NeuRRAM réside dans une méthode innovante de détection de la sortie en mémoire. Les approches conventionnelles utilisent la tension comme entrée et mesurent le courant comme résultat. Mais cela entraîne la nécessité de circuits plus complexes et plus gourmands en énergie. Dans la NeuRRAM, l’équipe a conçu un circuit neuronal qui détecte la tension et effectue une conversion analogique-numérique de manière économe en énergie. Cette détection en mode tension peut activer toutes les lignes et toutes les colonnes d’une matrice RRAM en un seul cycle de calcul, ce qui permet un parallélisme plus élevé.

Dans l’architecture NeuRRAM, les circuits neuronaux CMOS sont physiquement entrelacés avec les poids RRAM. Les connexions du neurone avec la matrice RRAM peuvent être configurées pour servir d’entrée ou de sortie du neurone. Les connexions du neurone avec la matrice RRAM peuvent être configurées pour servir d’entrée ou de sortie du neurone. Cela rend l’architecture plus facile à reconfigurer.

Pour s’assurer que la précision des calculs d’IA peut être préservée sur diverses architectures de réseaux neuronaux, les chercheurs ont développé un ensemble de techniques de co-optimisation des algorithmes matériels. Ces techniques ont été vérifiées sur différents réseaux neuronaux, notamment les réseaux neuronaux convolutifs, la mémoire à long terme et les machines de Boltzmann restreintes.

En tant que puce d’IA neuromorphique, NeuroRRAM effectue un traitement parallèle distribué sur 48 cœurs neurosynaptiques. Pour atteindre simultanément une grande polyvalence et une grande efficacité, NeuRRAM supporte le parallélisme des données en mappant une couche du modèle de réseau neuronal sur plusieurs cœurs pour une inférence parallèle sur plusieurs données. De même, NeuRRAM offre le parallélisme des modèles en mappant différentes couches d’un modèle sur différents cœurs et en effectuant l’inférence de manière pipelinée.

Une équipe de recherche internationale

Ces travaux sont le fruit du travail d’une équipe internationale de chercheurs.

L’équipe de l’UC San Diego a conçu les circuits CMOS qui mettent en œuvre les fonctions neuronales en s’interfaçant avec les matrices RRAM pour prendre en charge les fonctions synaptiques dans l’architecture de la puce, pour une efficacité et une polyvalence élevées. Wan, en étroite collaboration avec l’ensemble de l’équipe, a mis en œuvre la conception, caractérisé la puce, entraîné les modèles d’intelligence artificielle et réalisé les expériences. Wan a également développé une chaîne d’outils logiciels qui permet de faire correspondre les applications d’IA à la puce.

Le réseau de synapses RRAM et ses conditions de fonctionnement ont été largement caractérisés et optimisés à l’université de Stanford.

La matrice RRAM a été fabriquée et intégrée sur CMOS à l’université de Tsinghua.

L’équipe de Notre Dame a contribué à la fois à la conception et à l’architecture de la puce, ainsi qu’à la conception et à l’entraînement du modèle d’apprentissage automatique.

La recherche a débuté dans le cadre du projet Expeditions in Computing financé par la National Science Foundation sur le cortex visuel sur silicium à l’université de Penn State, avec le soutien financier continu du programme Science of AI de l’Office of Naval Research, de la Semiconductor Research Corporation et du programme JUMP de la DARPA, et de Western Digital Corporation.

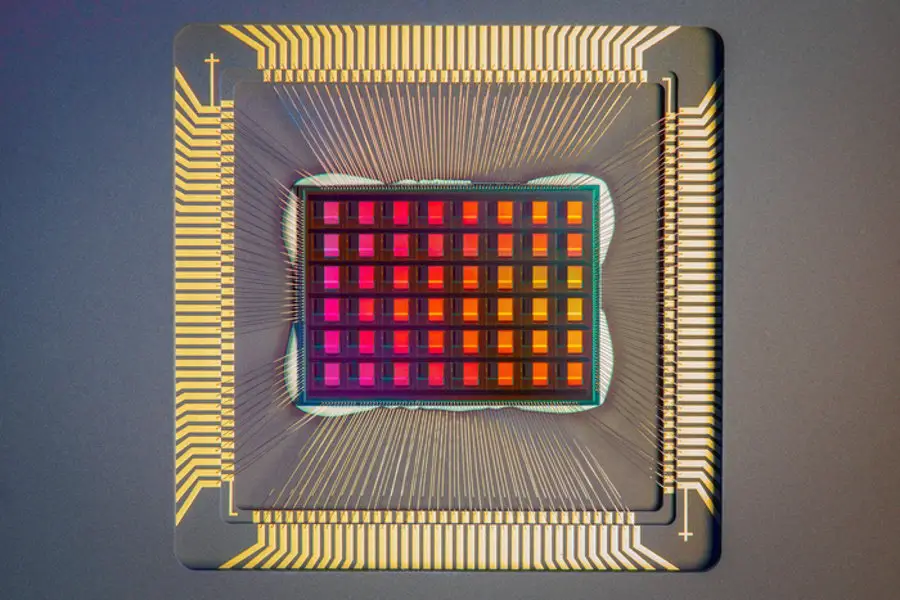

Une puce de calcul en mémoire basée sur une mémoire vive résistive

Crédit image : David Baillot/University of California San Diego

Weier Wan, Rajkumar Kubendran, Stephen Deiss, Siddharth Joshi et Gert Cauwenberghs, Université de Californie à San Diego.

Weier Wan, S. Burc Eryilmaz, Priyanka Raina, H-S Philip Wong, Université de Stanford

Clemens Schaefer, Siddharth Joshi, Université de Notre Dame

Rajkumar Kubendran, Université de Pittsburgh

Wenqiang Zhang, Dabin Wu, He Qian, Bin Gao, Huaqiang Wu, Université de Tsinghua

Auteurs correspondants : Wan, Gao, Joshi, Wu, Wong et Cauwenberghs