Kylie Foy | MIT Lincoln Laboratory

Face à la demande croissante de systèmes microélectroniques plus puissants et plus efficaces, l’industrie se tourne vers l’intégration 3D, c’est-à-dire l’empilement de puces les unes sur les autres. Cette architecture en couches verticales pourrait permettre aux processeurs à haute performance, comme ceux utilisés pour l’intelligence artificielle, d’être étroitement associés à d’autres puces hautement spécialisées pour la communication ou l’imagerie. Mais les technologues du monde entier sont confrontés à un défi majeur : comment empêcher ces piles de surchauffer.

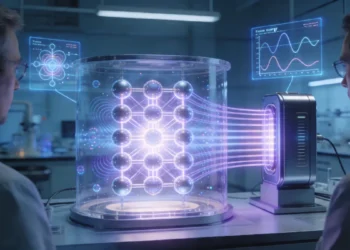

Le Lincoln Laboratory du MIT a mis au point une puce spécialisée pour tester et valider des solutions de refroidissement pour les piles de puces emballées. La puce dissipe une puissance extrêmement élevée, imitant les puces logiques à haute performance, pour générer de la chaleur à travers la couche de silicium et dans des points chauds localisés. Ensuite, lorsque les technologies de refroidissement sont appliquées à l’empilement, la puce mesure les changements de température. Insérée dans une pile, la puce permettra aux chercheurs d’étudier la façon dont la chaleur se déplace à travers les couches de la pile et d’évaluer les progrès accomplis pour les refroidir.

« Si vous n’avez qu’une seule puce, vous pouvez la refroidir par le haut ou par le bas. Mais si vous commencez à empiler plusieurs puces les unes sur les autres, la chaleur ne peut s’échapper nulle part. Il n’existe aujourd’hui aucune méthode de refroidissement qui permette à l’industrie d’empiler plusieurs de ces puces très performantes », indique Chenson Chen, qui a dirigé le développement de la puce avec Ryan Keech, tous deux du groupe Matériaux et microsystèmes avancés du laboratoire.

La puce de référence est désormais utilisée par HRL Laboratories, une société de recherche et de développement détenue conjointement par Boeing et General Motors, qui développe des systèmes de refroidissement pour les systèmes intégrés hétérogènes 3D (3DHI). L’intégration hétérogène fait référence à l’empilement de puces en silicium avec des puces non silicium, telles que les semi-conducteurs III-V utilisés dans les systèmes de radiofréquence (RF).

« Les composants RF peuvent être très chauds et fonctionner à des puissances très élevées, ce qui ajoute une couche supplémentaire de complexité à l’intégration 3D, d’où la nécessité de disposer de cette capacité de test », précise M. Keech.

L’Agence des projets de recherche avancée de défense (DARPA) a financé le développement par le laboratoire de la puce d’étalonnage pour soutenir le programme HRL. Toutes ces recherches s’inscrivent dans le cadre du programme Minitherms3D (Miniature Integrated Thermal Management Systems for 3D Heterogeneous Integration) de la DARPA.

Pour le ministère de la défense, les systèmes 3DHI ouvrent de nouvelles perspectives pour les systèmes critiques. Par exemple, 3DHI pourrait augmenter la portée des radars et des systèmes de communication, permettre l’intégration de capteurs avancés sur de petites plates-formes telles que les véhicules aériens sans équipage, ou permettre le traitement des données d’intelligence artificielle directement dans les systèmes sur le terrain plutôt que dans des centres de données distants.

La puce d’essai a été mise au point grâce à la collaboration de concepteurs de circuits, d’experts en essais électriques et de techniciens du laboratoire de microélectronique.

La puce remplit deux fonctions : générer de la chaleur et détecter la température. Pour générer de la chaleur, l’équipe a conçu des circuits capables de fonctionner à des densités de puissance très élevées, de l’ordre du kilowatt par centimètre carré, comparables à la demande de puissance prévue pour les puces à haute performance d’aujourd’hui et de demain. Ils ont également reproduit la disposition des circuits dans ces puces, ce qui a permis à la puce d’essai de servir de substitut réaliste.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

« Nous avons adapté notre technologie du silicium existante pour concevoir des radiateurs à l’échelle de la puce », explique M. Chen, qui apporte au programme des années d’expérience en matière d’intégration complexe et de conception de puces. Dans les années 2000, il a aidé le laboratoire à mettre au point la fabrication de circuits intégrés à deux et trois niveaux, menant les premiers développements de l’intégration 3D.

Les éléments chauffants de la puce émulent à la fois les niveaux de chaleur de fond au sein d’une pile et les points chauds localisés. Les points chauds se situent souvent dans les zones les plus enfouies et les plus inaccessibles d’une pile de puces, ce qui complique la tâche des concepteurs de puces 3D qui doivent déterminer si les systèmes de refroidissement, tels que les microcanaux délivrant un liquide froid, atteignent ces points et sont suffisamment efficaces.

C’est là qu’interviennent les éléments de détection de la température. La puce est distribuée avec ce que Chen compare à de « minuscules thermomètres » qui lisent la température à plusieurs endroits de la puce lorsque des liquides de refroidissement sont appliqués.

Ces thermomètres sont en fait des diodes, ou des commutateurs qui permettent au courant de circuler dans un circuit lorsqu’une tension est appliquée. Lorsque les diodes chauffent, le rapport courant/tension change. « Nous sommes en mesure de vérifier les performances d’une diode et de savoir si elle est à 200 degrés C, à 100 degrés C ou à 50 degrés C, par exemple », ajoute M. Keech. « Nous avons réfléchi de manière créative à la façon dont les dispositifs pouvaient tomber en panne à cause de la surchauffe, puis nous avons utilisé ces mêmes propriétés pour concevoir des outils de mesure utiles. »

Chen et Keech, ainsi que d’autres experts en conception, fabrication et essais électriques du laboratoire, collaborent désormais avec les chercheurs de HRL Laboratories pour coupler la puce avec de nouvelles technologies de refroidissement et intégrer ces technologies dans une pile 3DHI susceptible d’augmenter la puissance des signaux RF. « Nous devons refroidir l’équivalent thermique de plus de 190 unités centrales de traitement d’ordinateurs portables, mais dans la taille d’une seule unité centrale de traitement », a conclu Christopher Roper, co-chercheur principal à HRL, dans un récent communiqué de presse annonçant leur programme.

Selon M. Keech, la rapidité de livraison de la puce a été un défi relevé grâce au travail d’équipe à toutes les étapes de la conception, de la fabrication, des tests et de l’intégration hétérogène en 3D de la puce.

« Les architectures empilées sont considérées comme la prochaine frontière de la microélectronique », confirme-t-il. « Nous voulons aider le gouvernement américain à trouver des moyens de les intégrer efficacement et d’obtenir les meilleures performances possibles pour ces puces. »

Légende illustration : Cette plaquette de silicium contient des puces conçues pour tester les systèmes de refroidissement pour la microélectronique intégrée en 3D. Chaque puce comprend des circuits qui génèrent de la chaleur à l’intérieur d’un empilement 3D et mesurent la température lorsque des solutions de refroidissement sont appliquées. Crédit : Nicole Fandel