Les conceptions de micropuces peuvent être rationalisées en incorporant à la fois des concepts de haut niveau et des détails de câblage de bas niveau dans le même cadre de modélisation.

Un cadre de programmation pourrait rationaliser la conception des puces en comblant le fossé entre la conception conceptuelle et l’exécution pratique. Cela pourrait contribuer à relever le défi permanent auquel est confrontée l’industrie du matériel informatique, qui consiste à répondre à la demande d’appareils électroniques hautement performants et économes en énergie à des échelles toujours plus petites.

Cette demande représente depuis longtemps un défi : elle nécessite non seulement des transistors et des micropuces plus petits, mais aussi de nouvelles architectures matérielles innovantes qui offrent une disposition optimale des composants pour un flux et un traitement rapides des données. Cependant, la transformation d’une conception de haut niveau (c’est-à-dire exactement ce que nous attendons d’une puce) en détails de bas niveau pour du matériel pratique est un processus long et complexe qui nécessite de multiples itérations et une collaboration entre plusieurs équipes.

Lors du développement du cadre, appelé Assassyn (ASynchronous Semantics for Architectural Simulation and SYNthesis), les chercheurs, dont Jian Weng de KAUST, ont intégré à la fois la simulation architecturale et la mise en œuvre matérielle dans le monde réel.

Les systèmes informatiques numériques contiennent des modules de stockage d’informations interconnectés appelés registres. Les langages de niveau transfert de registre (RTL) tels que Verilog représentent les connexions entre les registres, tandis que les concepteurs se concentrent sur le comportement global du circuit. Cela crée un écart entre le processus de conception et la mise en œuvre réelle (le câblage effectif d’une puce).

« La plupart des recherches en matière de conception de puces adoptent deux styles distincts : les performances sont simulées, tandis que les caractéristiques de puissance par unité de surface sont estimées à travers une implémentation RTL distincte », indique M. Weng. « Cela signifie qu’il existe un décalage entre la conception et l’implémentation. Lors de la conception, vous pensez à effectuer des tâches à une étape et à « pousser » les données vers la suivante. Lors de la mise en œuvre en RTL, vous devez traduire cela en un style « pull » dans votre esprit : l’étape suivante attend le signal pour extraire les données. »

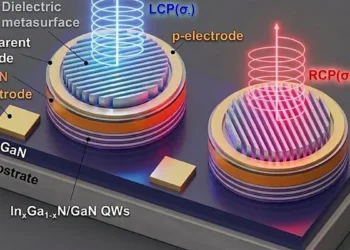

Les conceptions de puces les plus efficaces incluent des architectures « pipelining », qui permettent d’exécuter plusieurs tâches simultanément, en gardant de nombreux transistors actifs et en gagnant du temps, à l’instar d’une chaîne de montage en usine. L’un des principaux défis de la mise en œuvre du pipelining est la coordination entre les étapes.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

« Notre intuition est que le comportement des étapes du pipeline ne peut pas prendre effet immédiatement », précise M. Weng. Lui et ses collègues ont découvert que le secret pour unifier les étapes de conception et de mise en œuvre était que les événements ne devaient pas tous se produire en même temps.

« Dans Assassyn, nous utilisons la gestion asynchrone des événements, un paradigme de programmation largement adopté dans le développement de sites web », ajoute M. Weng. « Lorsque les fonctions sont appelées, elles ne sont pas exécutées toutes en même temps. Cette asynchronie est l’innovation clé qui permet à Assassyn de fonctionner. »

L’évaluation de l’équipe a montré qu’Assassyn générait des simulations RTL précises et performantes, permettant un gain de vitesse d’un ordre de grandeur par rapport aux modèles précédents. Pour éviter de réinventer la roue, le RTL généré par Assassyn peut s’intégrer directement dans les outils de conception existants. Les résultats ont montré que le RTL généré correspondait à la qualité des conceptions laborieusement réalisées à la main en termes de puissance, de surface de puce et de performances.

« De nombreux concepts de conception matérielle ont déjà convergé vers leurs points optimaux au cours des dernières décennies », explique M. Weng. « Au lieu de programmer manuellement chaque détail de la mise en œuvre matérielle, certains comportements courants peuvent être abstraits de manière générale. »

« Nous travaillons actuellement dans plusieurs directions, notamment la construction de nouveau matériel à l’aide d’Assassyn, la mise en place d’un meilleur écosystème pour Assassyn et l’extension de l’abstraction d’Assassyn pour la prochaine conception et implémentation matérielle optimale », conclut M. Weng.

Weng, J., Han, B., Gao, D., Gao, R., Zhang, W., Zhong, A., Xu, C., Xin, J., Luo, Y., Wills, L.W. & Canini, M. Assassyn: A unified abstraction for architectural simulation and implementation. ISCA ’25: Proceedings of the 52nd Annual International Symposium on Computer Architecture, 1464 – 1479 (2025).| article

Source : Kaust