Les six empilements de semi-conducteurs pour les micropuces hybrides à semi-conducteur à oxyde métallique complémentaire (CMOS) font progresser la miniaturisation et font tomber le précédent record de deux empilements.

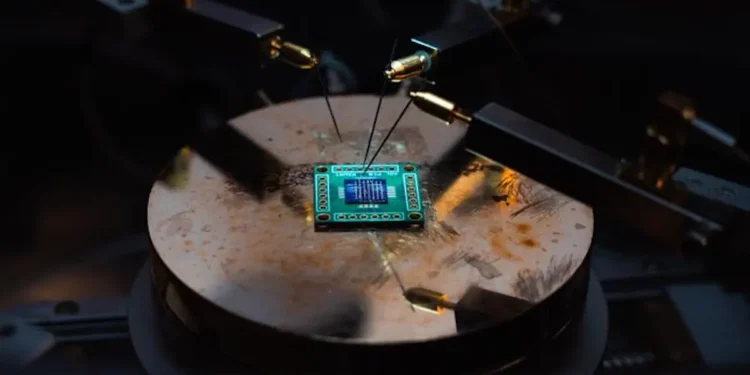

Les chercheurs de l’Université des sciences et technologies du roi Abdallah (KAUST, Arabie saoudite) ont établi un record dans la conception de micropuces en réalisant la première puce CMOS (semi-conducteur complémentaire à oxyde métallique) hybride à six couches pour l’électronique à grande surface. Aucune autre puce CMOS hybride dépassant deux couches n’ayant été signalée, cet exploit marque une nouvelle référence en matière de densité d’intégration et d’efficacité, ouvrant de nouvelles possibilités en matière de miniaturisation et de performances électroniques.

Parmi les technologies de micropuces, les micropuces CMOS sont présentes dans presque tous les appareils électroniques, des téléphones et téléviseurs aux satellites et appareils médicaux. Par rapport aux puces en silicium classiques, les micropuces CMOS hybrides sont plus prometteuses pour l’électronique à grande échelle. La miniaturisation électronique est cruciale pour l’électronique flexible, la santé intelligente et l’Internet des objets, mais les approches de conception actuelles atteignent leurs limites.

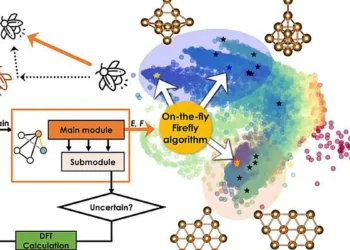

« Historiquement, l’industrie des semi-conducteurs s’est concentrée sur la réduction de la taille des transistors afin d’augmenter la densité d’intégration. Mais nous atteignons une limite quantique et les coûts montent en flèche », a déclaré Xiaohang Li, professeur associé à la KAUST, qui a dirigé l’étude et dirige le laboratoire avancé des semi-conducteurs de la KAUST. « Pour continuer à progresser, nous devons aller au-delà de la miniaturisation plane ; l’empilement vertical des transistors est une solution prometteuse. »

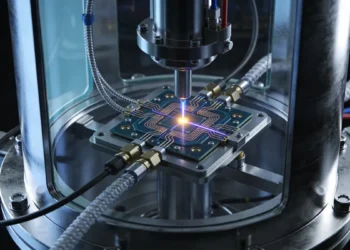

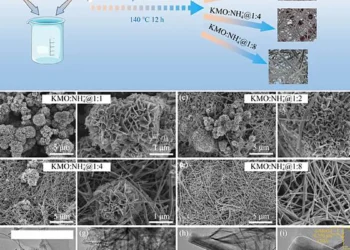

La fabrication de micropuces nécessite souvent des températures de plusieurs centaines de degrés Celsius, ce qui peut endommager les couches inférieures de la puce à mesure que de nouvelles couches sont ajoutées. Dans le processus KAUST, aucune étape de fabrication n’a dépassé 150 °C, et la plupart des étapes ont été réalisées à une température proche de la température ambiante.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

La surface des couches doit également être aussi lisse que possible. Les modifications apportées à la nouvelle conception ont permis de conserver des surfaces plus lisses que les processus de fabrication précédents. Pour l’empilement vertical, les couches doivent être correctement alignées pour une connexion optimale. Là encore, les scientifiques ont amélioré le processus de fabrication.

« Dans la conception des micropuces, l’objectif est de concentrer plus de puissance dans moins d’espace. En affinant plusieurs étapes de la fabrication, nous fournissons un modèle pour une mise à l’échelle verticale et une augmentation de la densité fonctionnelle bien au-delà des limites actuelles », a conclu Saravanan Yuvaraja, chercheur postdoctoral et premier auteur de l’article. Le professeur Martin Heeney et le professeur adjoint Thomas Anthopoulos de KAUST ont également contribué à cette étude.

Article : « Three-Dimensional Integrated Hybrid Complementary Circuits for Large-Area Electronics » – DOI : 10.1038/s41928-025-01469-0