Les transistors empilés verticalement émergent comme une solution novatrice pour accroître la puissance et l’efficacité des dispositifs électroniques. Les chercheurs basés en Arabie Saoudite ont développé une méthode révolutionnaire pour superposer les transistors, ouvrant ainsi de nouvelles possibilités pour l’industrie des semi-conducteurs.

L’omniprésence des technologies numériques dans notre quotidien engendre un besoin croissant de dispositifs électroniques plus puissants, efficaces et compacts. Les chercheurs de l’Université des Sciences et Technologies du Roi Abdullah ( KAUST ) ont relevé ce défi en explorant une nouvelle dimension dans la conception des transistors. Leur approche consiste à empiler verticalement les transistors, plutôt que de les disposer à plat comme c’est traditionnellement le cas.

Les transistors, composants essentiels de tous les appareils numériques, sont miniaturisés pour être intégrés dans des espaces toujours plus restreints. La technologie d’empilement vertical permet d’augmenter considérablement la densité de transistors, offrant ainsi une puissance de calcul accrue dans un volume réduit.

Une technologie prometteuse aux multiples avantages

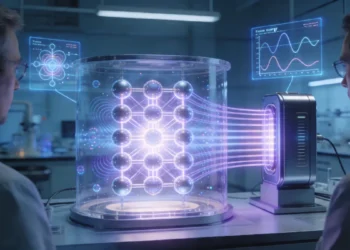

Saravanan Yuvaraja, chercheur postdoctoral au sein de l’équipe de Xiaohang Li, précise sa pensée : «Notre technologie de transistors à 10 couches devrait ouvrir la voie à une nouvelle génération de dispositifs électroniques plus rapides, plus compacts et plus performants que jamais.»

Bien que des approches d’empilement tridimensionnel de transistors aient déjà été explorées, la nouvelle technologie développée par KAUST surpasse les méthodes précédentes sur plusieurs aspects :

– Une commutation plus rapide

– Une consommation d’énergie réduite

– Des performances améliorées

La possibilité d’incorporer différentes architectures de transistors et portes logiques au sein d’une même pile permet la création de circuits complexes aux caractéristiques électriques finement ajustables.

L’oxyde d’indium : un matériau clé

Les chercheurs ont étudié le potentiel de matériaux semi-conducteurs spécifiques, notamment l’oxyde d’indium (In2O3). Yuvaraja souligne que ces matériaux présentent d’excellentes propriétés électroniques et peuvent être facilement traités à température ambiante.

L’innovation majeure de l’équipe réside dans l’adaptation de la technologie existante de fabrication de transistors à couches minces pour intégrer 10 couches de transistors à oxyde d’indium dans des piles verticales monolithiques compactes. Ces transistors empilés sont supportés par une plaquette conventionnelle de silicium/dioxyde de silicium, avec le polymère écologique Parylène-C servant de couches isolantes au sein des piles.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Des défis surmontés pour une technologie d’avenir

Le développement de cette technologie n’a pas été sans obstacles. Yuvaraja ajoute : «De nombreux défis ont nécessité des efforts persistants, une réflexion innovante et un travail méticuleux pour surmonter les obstacles qui se sont présentés à chaque étape.»

Parmi les principales difficultés rencontrées figuraient la recherche de matériaux compatibles pour l’empilement, le développement de techniques de lithographie appropriées et la conception de procédures de test efficaces.

Pour sa part, le professeur Li commente : «Notre réalisation offre des améliorations significatives par rapport aux alternatives existantes et établit une nouvelle référence dans la technologie des semi-conducteurs. Elle est hautement évolutive tant dans le plan X-Y que le long de l’axe Z, ce qui est crucial pour la poursuite de la loi de Moore.»

Perspectives futures

L’équipe de KAUST prévoit de poursuivre la miniaturisation de cette technologie tout en explorant de nouvelles façons d’améliorer encore son efficacité et ses performances. Les chercheurs anticipent que ces travaux pourraient avoir un impact sur une grande variété d’applications, notamment :

– Le calcul haute performance

– Les technologies mobiles et portables de nouvelle génération

– De nombreux dispositifs médicaux

Cette avancée dans le domaine des semi-conducteurs promet de repousser les limites de la puissance de calcul et de l’efficacité énergétique, ouvrant ainsi la voie à une nouvelle ère de l’électronique.

Légende illustration : Une technologie de transistor à 10 étages développée par le KAUST pourrait ouvrir la voie à la prochaine génération d’appareils électroniques qui seront plus rapides, plus compacts et plus performants que jamais. © 2024 KAUST.

Yuvaraja, S., Faber, H., Kumar, M., Xiao, N., García, G.I.M., Tang, X., Anthopoulos. T.D. & Li, X. Three-dimensional integrated metal-oxide transistors. Nature Electronics (2024).| article

Certaines mémoires sont déjà produites industriellement avec plus de 200 couches pour les Smartphones entre autres.

Il y a peut-être un intérêt pour les 10 couches que vous présentez mais pourquoi pas 8 ou 13 ?

C’est n’est peut-être pas le nombre de couches mais une astuce de géométrie des transistors réalisés en plusieurs couche, on ne voit pas laquelle. Avantage par rapport aux MBCFET, GAA, FinFET…