Une nouvelle ère pour l’informatique énergétiquement efficace compatible avec l’IA actuelle

Alors que la loi de Moore ralentit, une nouvelle approche de l’informatique pourrait changer la donne. Des chercheurs japonais et américains ont démontré un concept d’ordinateur énergétiquement efficace, compatible avec l’IA actuelle. Ce système utilise le comportement stochastique des dispositifs spintroniques à l’échelle nanométrique, ce qui le rend particulièrement adapté aux problèmes de calcul probabiliste.

Face au ralentissement de la loi de Moore, la demande en matériel spécifique à chaque domaine a augmenté. L’ordinateur probabiliste, avec ses blocs de construction naturellement stochastiques (bits probabilistes, ou p-bits), est un exemple représentatif en raison de sa capacité potentielle à traiter efficacement diverses tâches difficiles en matière d’apprentissage automatique (ML) et d’intelligence artificielle (IA).

De la même manière que les ordinateurs quantiques sont parfaitement adaptés aux problèmes intrinsèquement quantiques, les ordinateurs probabilistes à température ambiante sont appropriés pour les algorithmes intrinsèquement probabilistes. Ces derniers sont largement utilisés pour la formation des machines et les problèmes computationnels difficiles en optimisation, échantillonnage, etc.

Des avancées significatives

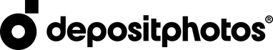

Récemment, des chercheurs de l’Université de Tohoku et de l’Université de Californie, Santa Barbara, ont démontré que des ordinateurs probabilistes robustes et entièrement asynchrones (sans horloge) peuvent être réalisés efficacement à grande échelle en utilisant un dispositif spintronique probabiliste appelé jonction tunnel magnétique stochastique (sMTJ) interférant avec des FPGA (Field Programmable Gate Arrays) puissants.

Jusqu’à présent, cependant, les ordinateurs probabilistes basés sur sMTJ n’ont été capables que de mettre en œuvre des réseaux neuronaux récurrents. Le développement d’un schéma pour mettre en œuvre des réseaux neuronaux ‘feedforward’ a été attendu.

« Comme les réseaux neuronaux feedforward sont à la base de la plupart des applications modernes de l’IA, l’augmentation des ordinateurs probabilistes dans cette direction devrait être une étape cruciale pour atteindre le marché et améliorer les capacités computationnelles de l’IA », a précisé le professeur Kerem Camsari, l’investigateur principal à l’Université de Californie, Santa Barbara.

En synthèse

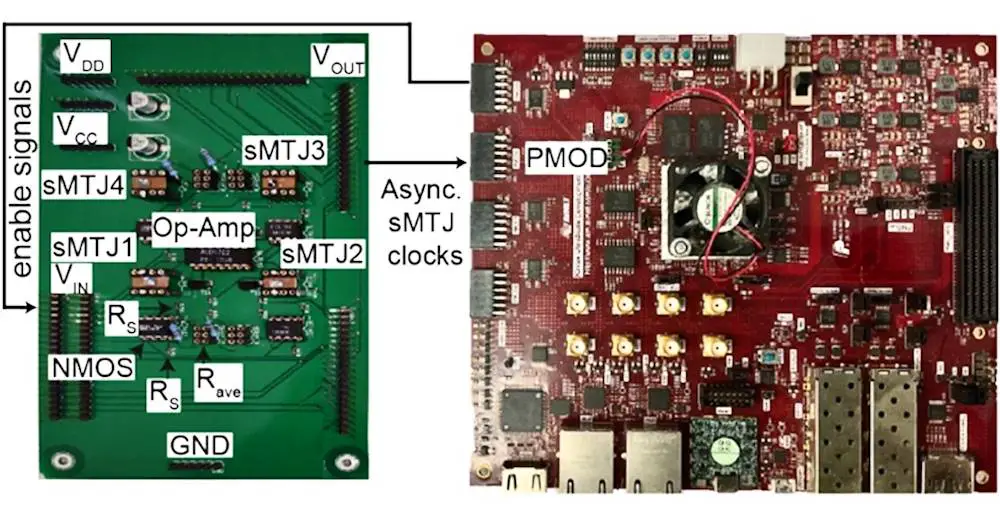

Les chercheurs ont fait deux avancées importantes. Premièrement, en s’appuyant sur des travaux antérieurs de l’équipe de l’Université de Tohoku sur les jonctions tunnel magnétiques stochastiques au niveau du dispositif, ils ont démontré les p-bits les plus rapides au niveau du circuit en utilisant des sMTJs dans le plan, fluctuant toutes les microsecondes environ, soit environ trois ordres de grandeur plus rapide que les rapports précédents.

Deuxièmement, en imposant un ordre de mise à jour au niveau du matériel informatique et en exploitant le parallélisme couche par couche, ils ont démontré l’opération de base du réseau bayésien comme exemple de réseaux neuronaux stochastiques ‘feedforward.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

« Les démonstrations actuelles sont à petite échelle, cependant, ces conceptions peuvent être mises à l’échelle en utilisant la technologie MRAM (Magnetic RAM) compatible CMOS, permettant des avancées significatives dans les applications d’apprentissage automatique tout en débloquant le potentiel pour une réalisation matérielle efficace des réseaux neuronaux profonds/convolutionnels », a conclu le professeur Shunsuke Fukami, l’investigateur principal à l’Université de Tohoku.

Pour une meilleure compréhension

Qu’est-ce que la loi de Moore ?

La loi de Moore est une observation selon laquelle le nombre de transistors sur un microprocesseur double environ tous les deux ans.

Qu’est-ce qu’un ordinateur probabiliste ?

Un ordinateur probabiliste est un type d’ordinateur qui utilise des bits probabilistes (p-bits) pour effectuer des calculs. Ces p-bits peuvent être dans un état de superposition, ce qui signifie qu’ils peuvent représenter à la fois 0 et 1 en même temps.

Qu’est-ce que la spintronique ?

La spintronique est un domaine de la physique qui étudie l’utilisation du spin des électrons (une propriété quantique) pour le stockage, le traitement et le transport de l’information dans les dispositifs électroniques.

Qu’est-ce qu’un réseau neuronal feedforward ?

Un réseau neuronal ‘feedforward’ est un type de réseau neuronal artificiel où les informations se déplacent dans une seule direction, de l’entrée à la sortie, sans boucles.

Qu’est-ce que la MRAM ?

La MRAM (Magnetic RAM) est une technologie de mémoire qui utilise des champs magnétiques pour stocker des informations. Elle est connue pour sa faible consommation d’énergie et sa haute densité de stockage.

Références

« Hardware Demonstration of Feedforward Stochastic Neural Networks with Fast MTJ-based p-bits » / Auteurs: Nihal Sanjay Singh, Shaila Niazi, Shuvro Chowdhury, Kemal Selcuk, Haruna Kaneko, Keito Kobayashi, Shun Kanai, Hideo Ohno, Shunsuke Fukami and Kerem Y. Camsari

Conférence: 69th Annual IEEE International Electron Devices Meeting (IEDM 2023)