Cette technologie peu coûteuse et évolutive permet d’intégrer de manière transparente des transistors en nitrure de gallium à grande vitesse sur une puce en silicium standard.

Le nitrure de gallium, matériau semi-conducteur avancé, sera probablement la clé de la prochaine génération de systèmes de communication à haut débit et de l’électronique de puissance nécessaire aux centres de données de pointe.

Malheureusement, le coût élevé du nitrure de gallium (GaN) et la spécialisation requise pour incorporer ce matériau semi-conducteur dans l’électronique conventionnelle ont limité son utilisation dans les applications commerciales.

Aujourd’hui, des chercheurs du MIT et d’ailleurs ont mis au point un nouveau processus de fabrication qui intègre des transistors GaN à haute performance sur des puces CMOS en silicium standard d’une manière peu coûteuse et évolutive, et compatible avec les fonderies de semi-conducteurs existantes.

Leur méthode consiste à construire de nombreux transistors minuscules sur la surface d’une puce GaN, à découper chaque transistor individuel, puis à coller juste le nombre nécessaire de transistors sur une puce en silicium à l’aide d’un processus à basse température qui préserve la fonctionnalité des deux matériaux.

Le coût reste minime puisque seule une infime quantité de matériau GaN est ajoutée à la puce, mais l’appareil qui en résulte peut bénéficier d’une augmentation significative des performances grâce à des transistors compacts et rapides. En outre, en séparant le circuit GaN en transistors discrets qui peuvent être répartis sur la puce de silicium, la nouvelle technologie est capable de réduire la température du système global.

Les chercheurs ont utilisé ce procédé pour fabriquer un amplificateur de puissance, un composant essentiel des téléphones portables, qui permet d’obtenir une force de signal et une efficacité supérieures à celles des dispositifs dotés de transistors en silicium. Dans un smartphone, cela pourrait améliorer la qualité des appels, augmenter la bande passante sans fil, améliorer la connectivité et prolonger la durée de vie de la batterie.

Comme cette méthode s’inscrit dans des procédures standard, elle pourrait améliorer l’électronique actuelle et les technologies futures. À terme, le nouveau schéma d’intégration pourrait même permettre des applications quantiques, car le GaN est plus performant que le silicium aux températures cryogéniques essentielles pour de nombreux types d’informatique quantique.

« Si nous pouvons réduire le coût, améliorer l’évolutivité et, en même temps, améliorer les performances du dispositif électronique, il est évident que nous devrions adopter cette technologie. Nous avons combiné le meilleur de ce qui existe dans le silicium avec la meilleure électronique possible en nitrure de gallium. Ces puces hybrides peuvent révolutionner de nombreux marchés commerciaux », détaille Pradyot Yadav, étudiant diplômé du MIT et auteur principal d’un article sur cette méthode.

Il est accompagné de ses collègues Jinchen Wang et Patrick Darmawi-Iskandar, étudiants diplômés du MIT, de John Niroula, post-doctorant au MIT, et des auteurs principaux Ulriche L. Rodhe, chercheur invité au Microsystems Technology Laboratories (MTL), Ruonan Han, professeur associé au département de génie électrique et d’informatique (EECS) et membre du MTL, Tomás Palacios, professeur Clarence J. LeBel d’EECS et directeur du MTL, ainsi que des collaborateurs de Georgia Tech et de l’Air Force Research Laboratory. La recherche a été récemment présentée au symposium de l’IEEE sur les circuits intégrés à radiofréquence.

Échanger des transistors

Le nitrure de gallium est le deuxième semi-conducteur le plus utilisé au monde, juste après le silicium, et ses propriétés uniques le rendent idéal pour des applications telles que l’éclairage, les systèmes radar et l’électronique de puissance.

Ce matériau existe depuis des décennies et, pour accéder à ses performances maximales, il est important que les puces en GaN soient connectées aux puces numériques en silicium, également appelées puces CMOS. Pour ce faire, certaines méthodes d’intégration lient des transistors GaN à une puce CMOS en soudant les connexions, mais cela limite la taille des transistors GaN. Plus les transistors sont petits, plus la fréquence à laquelle ils peuvent fonctionner est élevée.

D’autres méthodes intègrent une plaquette entière de nitrure de gallium sur une plaquette de silicium, mais l’utilisation d’une telle quantité de matériau est extrêmement coûteuse, d’autant plus que le GaN n’est nécessaire que dans quelques minuscules transistors. Le reste du matériau de la plaquette de GaN est gaspillé.

« Nous voulions combiner la fonctionnalité du GaN avec la puissance des puces numériques en silicium, sans devoir faire de compromis sur le coût ou la largeur de bande. Nous y sommes parvenus en ajoutant de minuscules transistors discrets en nitrure de gallium juste au-dessus de la puce en silicium », explique M. Yadav.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Les nouvelles puces sont le résultat d’un processus en plusieurs étapes.

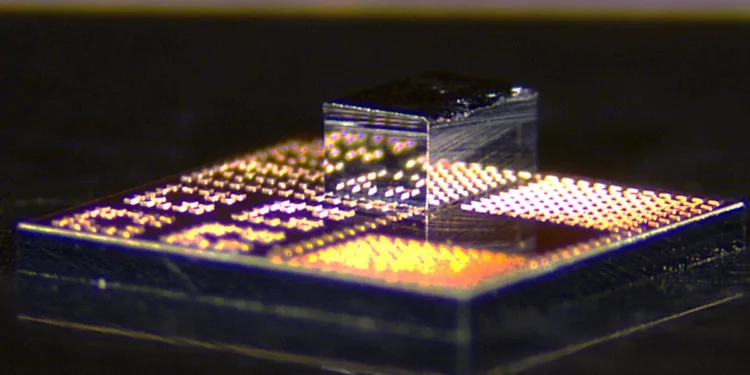

Tout d’abord, une collection très serrée de transistors minuscules est fabriquée sur toute la surface d’une plaquette de GaN. À l’aide d’une technologie laser très fine, ils découpent chacun d’entre eux à la taille du transistor, soit 240 par 410 microns, pour former ce qu’ils appellent un dielet (un micron est un millionième de la taille d’un transistor). (Un micron est un millionième de mètre.)

Chaque transistor est fabriqué avec de minuscules piliers de cuivre sur le dessus, qu’ils utilisent pour coller directement aux piliers de cuivre sur la surface d’une puce CMOS en silicium standard. La liaison cuivre-cuivre peut se faire à des températures inférieures à 400 degrés Celsius, ce qui est suffisamment bas pour ne pas endommager l’un ou l’autre matériau.

Les techniques actuelles d’intégration du GaN nécessitent des liaisons utilisant l’or, un matériau coûteux qui nécessite des températures beaucoup plus élevées et des forces de liaison plus fortes que le cuivre. Comme l’or peut contaminer les outils utilisés dans la plupart des fonderies de semi-conducteurs, il faut généralement des installations spécialisées.

« Nous voulions un procédé peu coûteux, à basse température et à faible force, et le cuivre l’emporte sur tous les aspects liés à l’or. En même temps, il a une meilleure conductivité », précise M. Yadav.

Un nouvel outil

Pour permettre le processus d’intégration, les chercheurs ont créé un nouvel outil spécialisé capable d’intégrer avec soin le transistor GaN extrêmement minuscule aux puces de silicium. L’outil utilise le vide pour maintenir le dielet pendant qu’il se déplace sur une puce en silicium, en se concentrant sur l’interface de liaison avec le cuivre avec une précision de l’ordre du nanomètre.

Ils ont utilisé une microscopie avancée pour surveiller l’interface, puis, lorsque le dielet est dans la bonne position, ils appliquent de la chaleur et de la pression pour lier le transistor GaN à la puce.

« Pour chaque étape du processus, je devais trouver un nouveau collaborateur qui savait comment réaliser la technique dont j’avais besoin, apprendre de lui, puis l’intégrer dans ma plateforme. Cela a représenté deux ans d’apprentissage permanent », ajoute M. Yadav.

Une fois que les chercheurs ont perfectionné le processus de fabrication, ils l’ont démontré en développant des amplificateurs de puissance, c’est-à-dire des circuits de radiofréquence qui amplifient les signaux sans fil.

Leurs dispositifs ont permis d’obtenir une bande passante plus large et un meilleur gain que les dispositifs fabriqués avec des transistors en silicium traditionnels. Chaque puce compacte a une surface inférieure à un demi-millimètre carré.

En outre, comme la puce de silicium qu’ils ont utilisée pour leur démonstration est basée sur le FinFET Intel 16 22nm à la pointe de la métallisation et des options passives, ils ont pu incorporer des composants souvent utilisés dans les circuits de silicium, tels que des condensateurs de neutralisation. Le gain de l’amplificateur s’en est trouvé considérablement amélioré, ce qui l’a rapproché de la prochaine génération de technologies sans fil.

« Pour faire face au ralentissement de la loi de Moore dans la mise à l’échelle des transistors, l’intégration hétérogène est apparue comme une solution prometteuse pour la mise à l’échelle continue des systèmes, la réduction du facteur de forme, l’amélioration de l’efficacité énergétique et l’optimisation des coûts. Dans le domaine de la technologie sans fil en particulier, l’intégration étroite de semi-conducteurs composés avec des tranches de silicium est essentielle pour réaliser des systèmes unifiés de circuits intégrés frontaux, de processeurs de bande de base, d’accélérateurs et de mémoire pour les plates-formes antennes-IA de la prochaine génération. Ce travail constitue une avancée significative en démontrant l’intégration 3D de plusieurs puces GaN avec des CMOS en silicium et repousse les limites des capacités technologiques actuelles », conclut Atom Watanabe, chercheur scientifique chez IBM, qui n’a pas participé à la rédaction de cet article.

Ce travail est soutenu, en partie, par le ministère américain de la défense par l’intermédiaire du programme de bourses NDSEG (National Defense Science and Engineering Graduate) et par CHIMES, l’un des sept centres de JUMP 2.0, un programme de la Semiconductor Research Corporation du ministère de la défense et de la Defense Advanced Research Projects Agency (DARPA). La fabrication a été réalisée dans des installations du MIT.Nano, du laboratoire de recherche de l’armée de l’air et de Georgia Tech.

Article : « 3D-Millimeter Wave Integrated Circuit (3D-mmWIC): A Gold-Free 3D-Integration Platform for Scaled RF GaN-on-Si Dielets with Intel 16 Si CMOS » – DOI : rfic-technical-sessions

Source : MIT