Les processeurs de recuit simulé sont des outils prometteurs pour résoudre des problèmes d’optimisation combinatoire complexes. Une équipe de chercheurs de l’Université des Sciences de Tokyo a récemment développé un processeur évolutif innovant qui divise les calculs entre plusieurs puces LSI, ouvrant la voie à de nouvelles applications dans des domaines variés.

Dans le contexte des technologies CMOS, un couplage complet des composants des processeurs de recuit simulé est essentiel. Cependant, la complexité de ce couplage a un impact direct sur l’évolutivité des processeurs, limitant ainsi leur potentiel d’application à grande échelle.

Comme l’explique le Professeur Takayuki Kawahara, qui a dirigé cette étude publiée le 30 janvier 2024 dans IEEE Access, « Nous voulons réaliser un traitement avancé de l’information directement à la périphérie, plutôt que dans le cloud, ou effectuer un prétraitement à la périphérie pour le cloud. »

Une architecture innovante et évolutive

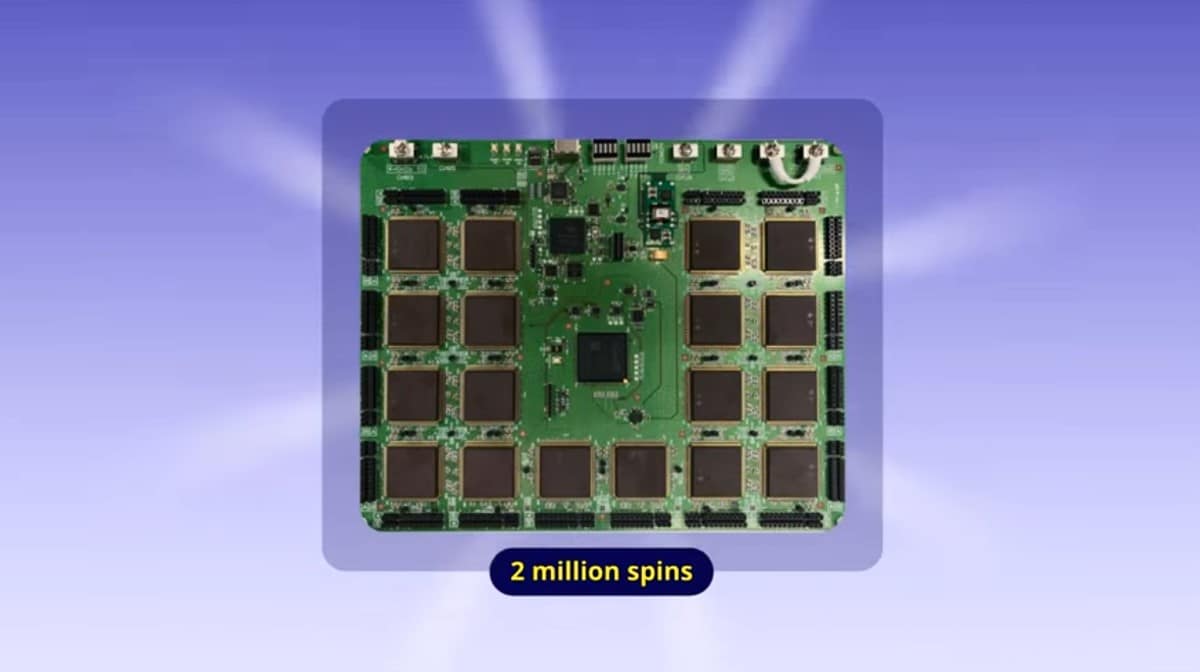

L’équipe de recherche a mis au point un processeur de recuit simulé évolutif utilisant 36 puces LSI de calcul en technologie CMOS 22nm et un FPGA de contrôle. Cette technologie permet de construire des systèmes semi-conducteurs entièrement couplés à grande échelle suivant le modèle d’Ising, avec 4096 spins.

Le processeur intègre deux technologies distinctes développées à l’Université des Sciences de Tokyo : une «méthode de fil de spin» permettant 8 recherches de solutions en parallèle, et une technique réduisant d’environ moitié les besoins en puces par rapport aux méthodes conventionnelles. Ses besoins en énergie sont également modestes, fonctionnant à 10MHz avec une consommation de 2,9W (1,3W pour la partie centrale).

Des performances impressionnantes

En termes de rapport performance/puissance, le processeur a surpassé de 2 306 fois la simulation d’un système d’Ising entièrement couplé sur un PC (i7, 3,6GHz) utilisant l’émulation de recuit simulé. De plus, il a dépassé de 2 186 fois le CPU principal et la puce arithmétique.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Selon le Professeur Kawahara, qui envisage l’implémentation sociale de cette technologie, « À l’avenir, nous développerons cette technologie pour un effort de recherche conjoint visant un système LSI avec la puissance de calcul d’un ordinateur quantique de niveau 2050 pour résoudre des problèmes d’optimisation combinatoire. L’objectif est d’y parvenir sans avoir besoin de climatisation, de gros équipements ou d’infrastructure cloud, en utilisant les processus semi-conducteurs actuels. »

Vers de nouvelles industries numériques

La vérification réussie de ce processeur suggère la possibilité d’une capacité accrue. L’équipe vise à atteindre 2 millions de spins d’ici 2030 et à explorer la création de nouvelles industries numériques utilisant cette technologie.

Les chercheurs ont donc développé un processeur de recuit simulé évolutif et entièrement couplé intégrant 4096 spins sur une seule carte avec 36 puces CMOS. Des innovations clés, notamment la réduction des puces et les opérations parallèles pour des recherches de solutions simultanées, ont joué un rôle crucial dans ce développement prometteur pour de nombreuses applications pratiques.

Article : « Scalable Fully-Coupled Annealing Processing System Implementing 4096 Spins Using 22nm CMOS LSI » – DOI: 10.1109/ACCESS.2024.3360034