La miniaturisation des composants électroniques franchit une nouvelle étape grâce à une innovation dans la fabrication de transistors verticaux. Les implications de cette avancée technologique pour l’industrie électronique sont considérables, promettant des appareils plus compacts et plus performants.

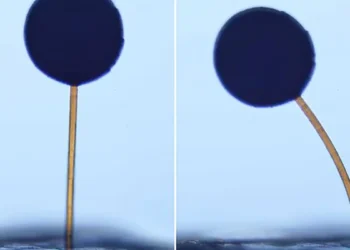

Une équipe de chercheurs du Laboratoire d’analyse et d’architecture des systèmes (LAAS-CNRS) a développé une méthode novatrice pour la fabrication de transistors verticaux miniaturisés. Cette technique, basée sur l’utilisation de nanofils de silicium, permet la création de contacts métalliques d’une fiabilité et d’une performance jusqu’alors inégalées.

L’innovation majeure réside dans l’abandon de la résine photosensible traditionnellement utilisée pour le dépôt sélectif du métal. Les scientifiques ont opté pour une approche alternative. Une couche métallique est déposée à la base des nanofils, puis structurée par un procédé de gravure couramment employé dans l’industrie des semiconducteurs.

Des performances améliorées et une fiabilité accrue

La nouvelle méthode présente des avantages significatifs. Elle permet notamment de réduire la résistance électrique des contacts métalliques, améliorant ainsi sensiblement leurs performances. De plus, la reproductibilité du procédé s’avère excellente, garantissant une uniformité des caractéristiques d’un transistor à l’autre.

Le potentiel de la technologie a été démontré par les chercheurs. Des portes logiques NOR et NAND, éléments fondamentaux de la plupart des fonctions logiques dans les circuits intégrés, ont été réalisées. L’utilisation de transistors verticaux de taille nanométrique, avec des longueurs de grille inférieures à 20 nm, pourrait permettre de réduire d’environ 50% la surface du substrat utilisée par rapport aux technologies planaires actuelles. Cette avancée représente un pas important vers la densification des circuits intégrés.

La prochaine étape des travaux est déjà envisagée par les chercheurs : la réalisation d’empilements de plusieurs niveaux de transistors verticaux. Cette approche pourrait conduire à une augmentation encore plus significative de la densité des composants électroniques.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Répercussions sur l’industrie électronique

Les implications de cette avancée technologique sont considérables pour l’industrie électronique. La possibilité de créer des circuits plus compacts ouvre de nouvelles possibilités pour des appareils électroniques plus petits, plus puissants et potentiellement plus économes en énergie.

Les résultats de cette recherche ont été publiés dans la revue scientifique ACS Nano Letters. La publication souligne l’importance de cette avancée pour la communauté scientifique et l’industrie des semiconducteurs. Cette innovation dans la fabrication de transistors verticaux marque une étape importante dans l’évolution de l’électronique. Elle laisse entrevoir un futur où les appareils électroniques seront encore plus intégrés dans notre quotidien, offrant des performances accrues dans des formats toujours plus compacts.

Légende illustration : Illustration de circuits de portes logiques réalisés à l’aide de transistors verticaux 3D, comportant des grilles entourantes nanométriques (en rouge), et exploitant de nouvelles possibilités de distribution des contacts en 3D (en doré). ©G. Larrieu, LAAS-CNRS

Article : « Logic Gates Based on 3D Vertical Junctionless Gate-All-Around Transistors with Reliable Multilevel Contact Engineering ».

Abhishek Kumar, Jonas Müller, Sylvain Pelloquin, Aurélie Lecestre, and Guilhem Larrieu. ACS Nano Letters 2024, 24, 26, 7825–7832. 10.1021/acs.nanolett.3c04180