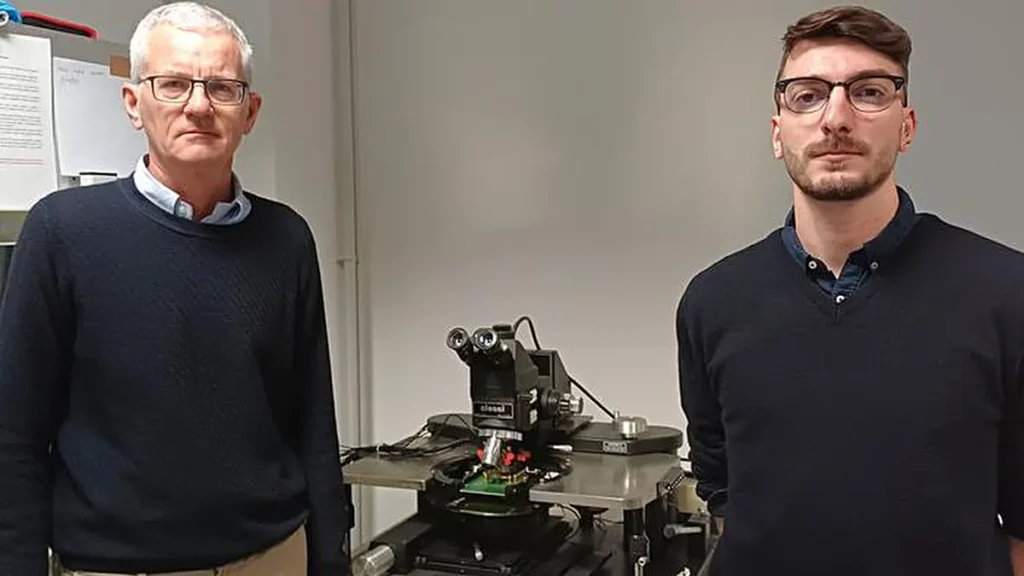

Réduire drastiquement la consommation d’énergie tout en accélérant le traitement de grandes quantités de données. Tel est l’objectif de la nouvelle puce développée par un groupe de chercheurs du Département d’Électronique, d’Information et de Bioingénierie – DEIB du Politecnico di Milano, dirigé par le professeur Daniele Ielmini, et présentée dans l’étude publiée dans la prestigieuse revue Nature Electronics, avec le chercheur Piergiulio Mannocci comme premier auteur.

Les travaux sont nés dans le cadre du projet ANIMATE (ANalogue In-Memory computing with Advanced device TEchnology), qui a obtenu une bourse ERC Advanced en 2022 et s’est appuyé sur les recherches préliminaires de Daniele Ielmini sur le CL-IMC (Closed-Loop In-Memory Computing) et les opportunités qu’il pourrait offrir, à savoir une résolution plus rapide des calculs et une utilisation jusqu’à 5 000 fois moins d’énergie que les ordinateurs numériques. L’objectif du projet ANIMATE était de développer la technologie pour le dispositif, les circuits et architectures système, et l’ensemble des applications pour valider le CL-IMC.

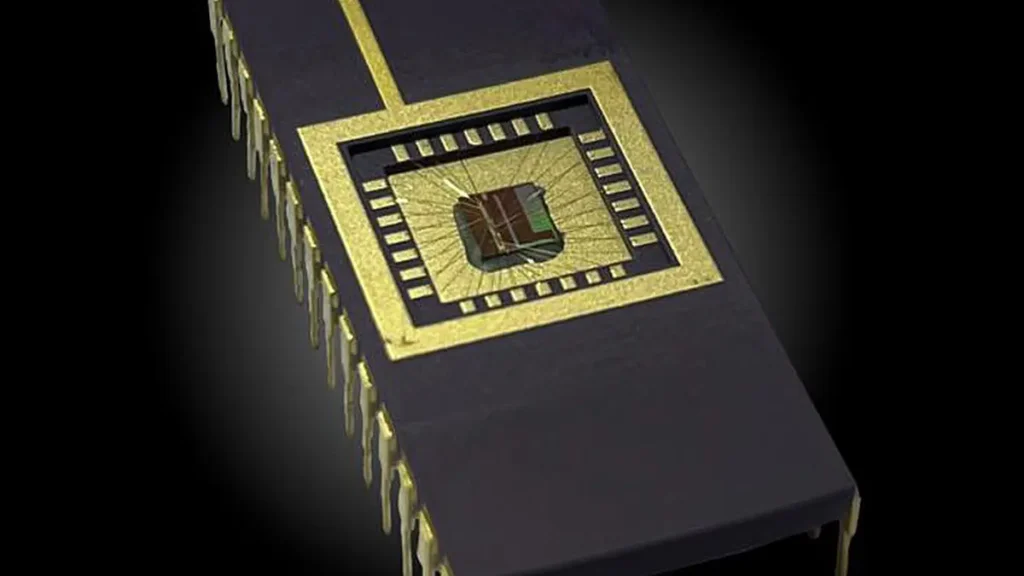

La puce obtenue utilise le calcul en mémoire, qui vise à surmonter une limitation des ordinateurs : la nécessité de déplacer continuellement les données entre la mémoire et le processeur. En éliminant ce « trafic » interne, les systèmes deviennent plus rapides et plus efficaces énergétiquement. Dans l’étude récemment publiée, l’équipe du DEIB a présenté un accélérateur analogique entièrement intégré pour résoudre des systèmes d’équations linéaires et non linéaires conçu avec la technologie CMOS (Complementary Metal-Oxide-Semiconductor), mise en œuvre de manière standard pour la production de circuits intégrés en silicium.

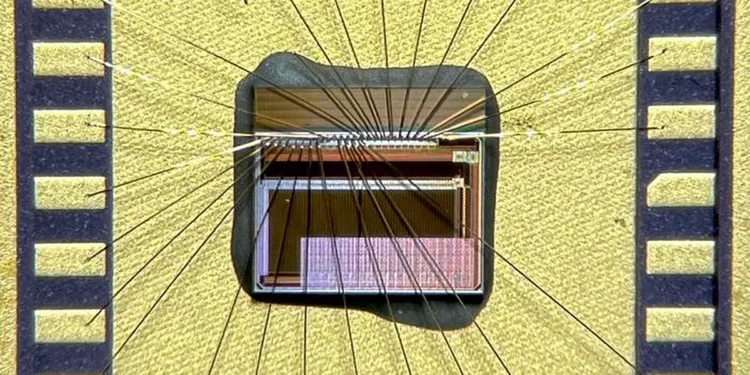

Le dispositif utilise deux matrices 64×64 de mémoires résistives programmables : une matrice est une sorte de « grille ordonnée » composée d’éléments identiques disposés en lignes et colonnes, semblable à du papier millimétré, où chaque intersection entre une ligne et une colonne représente une cellule mémoire. Les cellules sont basées sur la technologie SRAM (Static Random-Access Memory), un type de mémoire rapide et stable qui est ici combiné à des résistances intégrées pour programmer différents niveaux de résistance. L’architecture est complétée par un modèle innovant de traitement analogique qui utilise des composants intégrés dans la puce tels que des amplificateurs opérationnels et des convertisseurs analogique-numérique.

L’ensemble permet au système de gérer des calculs complexes directement dans la structure de la mémoire, évitant ainsi de devoir déplacer les données vers un processeur externe, réduisant ainsi considérablement les temps de calcul. Lors des tests, la puce a atteint une précision similaire à celle des systèmes numériques conventionnels, mais avec une consommation électrique plus faible, une latence de calcul réduite et une empreinte plus petite sur le silicium.

Daniele Ielmini, membre du DEIB et chef du groupe de recherche, a expliqué : « La puce intégrée démontre la faisabilité à l’échelle industrielle d’un concept révolutionnaire comme le calcul analogique en mémoire. Nous travaillons déjà à mettre en œuvre cette innovation dans des applications réelles pour réduire les coûts énergétiques du calcul, notamment dans le domaine de l’intelligence artificielle ».

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Piergiulio Mannocci, chercheur au DEIB et premier auteur, a commenté : « Ce travail est le fruit d’une collaboration internationale entre le monde universitaire et l’industrie qui a également impliqué l’Université de Pékin, une équipe diversifiée comprenant professeurs, chercheurs, doctorants et étudiants, et démontre le potentiel du calcul analogique en mémoire pour des applications haute performance et économes en énergie. »

L’étude représente une étape importante vers des dispositifs plus compacts, plus rapides et plus durables, ouvrant de nouvelles perspectives pour la recherche et l’industrie. Le calcul en mémoire est une solution idéale, en effet, dans des contextes exigeant des performances élevées et une haute efficacité énergétique comme l’intelligence artificielle, le traitement de grands volumes de données et les systèmes de communication sans fil de nouvelle génération. Les applications vont de la robotique aux centres de données et des systèmes de navigation aux réseaux de télécommunications avancés, tels que la 5G et les futures technologies 6G.

Article : A fully integrated analogue closed-loop in-memory computing accelerator based on static random-access memory – Journal : Nature Electronics – Méthode : Computational simulation/modeling – DOI : Lien vers l’étude

Source : Ecole Polytechnique de Milan