Hussam Amrouch, professeur à l’Université Technique de Munich (TUM), a développé une architecture prête pour l’IA qui est deux fois plus puissante que les approches comparables de calcul en mémoire. Cette avancée pourrait s’avérer utile pour l’IA générative, les algorithmes d’apprentissage profond et les applications robotiques dans quelques années.

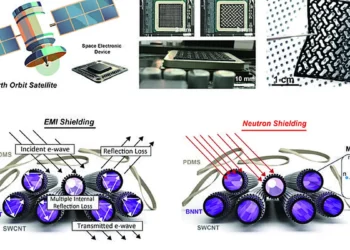

Le professeur Amrouch applique un nouveau paradigme de calcul en utilisant des circuits spéciaux appelés transistors à effet de champ ferroélectrique (FeFETs). Contrairement aux puces précédentes où seules les calculs étaient effectués sur les transistors, ceux-ci sont maintenant également le lieu de stockage des données.

Cela permet de gagner du temps et de l’énergie. « En conséquence, les performances des puces sont également améliorées », explique Hussam Amrouch.

Des transistors miniaturisés

Les transistors sur lesquels il effectue des calculs et stocke des données mesurent seulement 28 nanomètres, avec des millions d’entre eux placés sur chacune des nouvelles puces d’IA. Les puces du futur devront être plus rapides et plus efficaces que les précédentes.

Par conséquent, elles ne peuvent pas chauffer aussi rapidement. C’est essentiel si elles doivent supporter des applications comme les calculs en temps réel lorsqu’un drone est en vol, par exemple.

Des puces plus puissantes

La nouvelle puce d’IA, développée en collaboration entre Bosch et Fraunhofer IMPS et soutenue dans le processus de production par la société américaine GlobalFoundries, peut délivrer 885 TOPS/W. Cela la rend deux fois plus puissante que les puces d’IA comparables, y compris une puce MRAM de Samsung.

Les puces CMOS, qui sont maintenant couramment utilisées, fonctionnent dans la plage de 10-20 TOPS/W.

En synthèse

Le professeur Amrouch a développé une architecture prête pour l’IA qui est deux fois plus puissante que les approches comparables de calcul en mémoire. Cette avancée pourrait s’avérer utile pour l’IA générative, les algorithmes d’apprentissage profond et les applications robotiques dans quelques années.

Il estime toutefois qu’il faudra encore trois à cinq ans avant que les premières puces en mémoire adaptées aux applications réelles ne soient disponibles. Cela souligne l’importance de la collaboration interdisciplinaire avec des chercheurs de diverses disciplines telles que l’informatique et l’ingénierie électrique.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Pour une meilleure compréhension

Qu’est-ce que l’architecture prête pour l’IA développée par Hussam Amrouch ?

C’est une architecture qui utilise un nouveau paradigme de calcul avec des circuits spéciaux appelés transistors à effet de champ ferroélectrique (FeFETs). Ces transistors permettent à la fois le calcul et le stockage des données, ce qui améliore les performances des puces.

Quelle est la taille des transistors utilisés ?

Les transistors sur lesquels le professeur Amrouch effectue des calculs et stocke des données mesurent seulement 28 nanomètres.

Quelle est la performance de la nouvelle puce d’IA ?

La nouvelle puce d’IA peut délivrer 885 TOPS/W, ce qui la rend deux fois plus puissante que les puces d’IA comparables.

Quand les premières puces en mémoire adaptées aux applications réelles seront-elles disponibles ?

Le professeur Amrouch estime qu’il faudra encore trois à cinq ans avant que les premières puces en mémoire adaptées aux applications réelles ne soient disponibles.

Quelle est l’importance de la collaboration interdisciplinaire dans ce domaine ?

La collaboration interdisciplinaire avec des chercheurs de diverses disciplines telles que l’informatique et l’ingénierie électrique est essentielle pour répondre aux exigences de sécurité de l’industrie et pour adapter la technologie aux critères spécifiques de chaque secteur.

Article original publié dans la revue Nature par le professeur Hussam Amrouch de l’Université Technique de Munich (TUM).

Taha Soliman, Swetaki Chatterjee, Nellie Laleni, Franz Müller, Tobias Kirchner, Norbert Wehn, Thomas Kämpfe, Yogesh Singh Chauhan & Hussam Amrouch First demonstration of in-memory computing crossbar using multi-level Cell FeFET Nature Communications volume 14, Article number: 6348 (2023)

Légende illustration principale : Le professeur Hussam Amrouch développe une puce d’IA puissante pour les applications à forte consommation d’énergie.