Des chercheurs du MIT ont développé une nouvelle méthode de fabrication qui pourrait permettre la production d’électronique plus économe en énergie en empilant plusieurs composants fonctionnels au-dessus d’un circuit existant.

Dans les circuits traditionnels, les dispositifs logiques qui effectuent les calculs, comme les transistors, et les dispositifs de mémoire qui stockent les données sont construits comme des composants séparés, forçant les données à voyager en va-et-vient entre eux, ce qui gaspille de l’énergie.

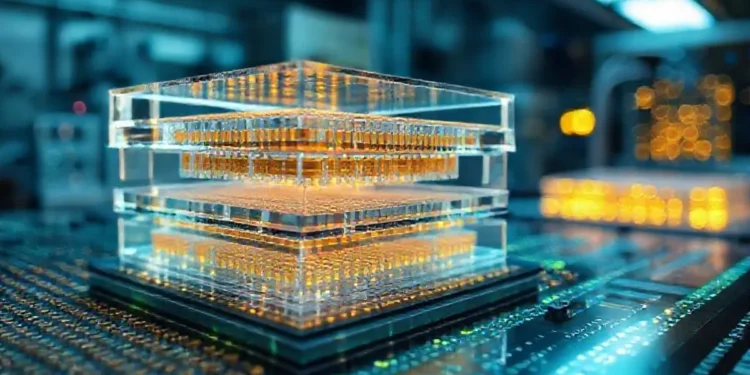

Cette nouvelle plateforme d’intégration électronique permet aux scientifiques de fabriquer des transistors et des dispositifs de mémoire dans une pile compacte sur une puce semi-conductrice. Cela élimine une grande partie de cette énergie gaspillée tout en augmentant la vitesse de calcul.

La clé de cette avancée est un matériau nouvellement développé aux propriétés uniques et une approche de fabrication plus précise qui réduit le nombre de défauts dans le matériau. Cela permet aux chercheurs de fabriquer des transistors extrêmement petits avec une mémoire intégrée qui peuvent fonctionner plus rapidement que les dispositifs les plus avancés tout en consommant moins d’électricité que des transistors similaires.

En améliorant l’efficacité énergétique des dispositifs électroniques, cette nouvelle approche pourrait aider à réduire la consommation d’électricité croissante du calcul, en particulier pour les applications exigeantes comme l’IA générative, l’apprentissage profond et les tâches de vision par ordinateur.

« Nous devons minimiser la quantité d’énergie que nous utilisons pour l’IA et d’autres calculs centrés sur les données à l’avenir, car ce n’est tout simplement pas durable. Nous aurons besoin de nouvelles technologies comme cette plateforme d’intégration pour poursuivre ces progrès », affirme Yanjie Shao, un postdoctorant du MIT et auteur principal de deux articles sur ces nouveaux transistors.

La nouvelle technique est décrite dans deux articles (dont un sur invitation) qui ont été présentés lors de la réunion IEEE International Electron Devices Meeting. Shao est rejoint sur les articles par les auteurs principaux Jesús del Alamo, le professeur Donner d’ingénierie au département de génie électrique et d’informatique (EECS) du MIT ; Dimitri Antoniadis, le professeur Ray et Maria Stata de génie électrique et d’informatique au MIT ; ainsi que d’autres collaborateurs du MIT, de l’Université de Waterloo et de Samsung Electronics.

Retourner le problème

Les puces CMOS (semi-conducteur à oxyde de métal complémentaire) standard ont traditionnellement un front end, où les composants actifs comme les transistors et les condensateurs sont fabriqués, et un back end qui comprend des fils appelés interconnexions et d’autres liaisons métalliques qui connectent les composants de la puce.

Mais une partie de l’énergie est perdue lorsque les données voyagent entre ces liaisons, et de légers désalignements peuvent nuire aux performances. Empiler des composants actifs réduirait la distance que les données doivent parcourir et améliorerait l’efficacité énergétique d’une puce.

Typiquement, il est difficile d’empiler des transistors en silicium sur une puce CMOS car la haute température requise pour fabriquer des dispositifs supplémentaires sur le front end détruirait les transistors existants en dessous.

Les chercheurs du MIT ont retourné ce problème, développant une technique d’intégration pour empiler des composants actifs sur le back end de la puce à la place.

« Si nous pouvons utiliser cette plateforme back-end pour ajouter des couches actives supplémentaires de transistors, pas seulement des interconnexions, cela rendrait la densité d’intégration de la puce beaucoup plus élevée et améliorerait son efficacité énergétique », explique Shao.

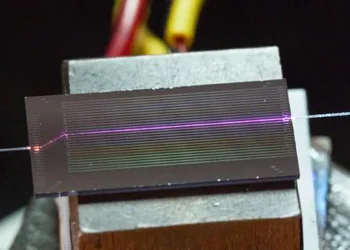

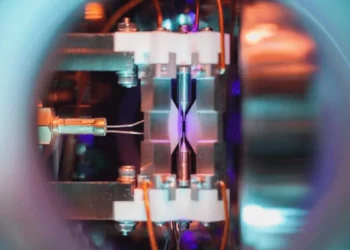

Les chercheurs ont accompli cela en utilisant un nouveau matériau, l’oxyde d’indium amorphe, comme couche de canal active de leur transistor back-end. La couche de canal active est l’endroit où les fonctions essentielles du transistor ont lieu.

Newsletter Enerzine

Recevez les meilleurs articles

Énergie, environnement, innovation, science : l’essentiel directement dans votre boîte mail.

Grâce aux propriétés uniques de l’oxyde d’indium, ils peuvent « faire croître » une couche extrêmement fine de ce matériau à une température d’environ seulement 150 degrés Celsius sur le back end d’un circuit existant sans endommager le dispositif sur le front end.

Parfaire le processus

Ils ont soigneusement optimisé le processus de fabrication, ce qui minimise le nombre de défauts dans une couche de matériau d’oxyde d’indium d’environ seulement 2 nanomètres d’épaisseur.

Quelques défauts, connus sous le nom de lacunes d’oxygène, sont nécessaires pour que le transistor s’allume, mais avec trop de défauts, il ne fonctionne pas correctement. Ce processus de fabrication optimisé permet aux chercheurs de produire un transistor extrêmement petit qui fonctionne rapidement et proprement, éliminant une grande partie de l’énergie supplémentaire requise pour faire basculer un transistor entre l’état éteint et allumé.

S’appuyant sur cette approche, ils ont également fabriqué des transistors back-end avec mémoire intégrée d’environ seulement 20 nanomètres de taille. Pour ce faire, ils ont ajouté une couche de matériau appelé oxyde d’hafnium-zirconium ferroélectrique comme composant de mémoire.

Ces transistors de mémoire compacts ont démontré des vitesses de commutation de seulement 10 nanosecondes, atteignant la limite des instruments de mesure de l’équipe. Cette commutation nécessite également une tension beaucoup plus faible que les dispositifs similaires, réduisant la consommation d’électricité.

Et parce que les transistors de mémoire sont si petits, les chercheurs peuvent les utiliser comme plateforme pour étudier la physique fondamentale des unités individuelles d’oxyde d’hafnium-zirconium ferroélectrique.

« Si nous pouvons mieux comprendre la physique, nous pouvons utiliser ce matériau pour de nombreuses nouvelles applications. L’énergie qu’il utilise est très minime, et cela nous donne beaucoup de flexibilité dans la façon dont nous pouvons concevoir les dispositifs. Cela pourrait vraiment ouvrir de nombreuses nouvelles voies pour l’avenir », déclare Shao.

Les chercheurs ont également collaboré avec une équipe de l’Université de Waterloo pour développer un modèle de performance des transistors back-end, ce qui est une étape importante avant que les dispositifs puissent être intégrés dans des circuits plus grands et des systèmes électroniques.

À l’avenir, ils souhaitent s’appuyer sur ces démonstrations en intégrant des transistors de mémoire back-end sur un seul circuit. Ils veulent également améliorer les performances des transistors et étudier comment contrôler plus finement les propriétés de l’oxyde d’hafnium-zirconium ferroélectrique.

« Maintenant, nous pouvons construire une plateforme d’électronique polyvalente sur le back end d’une puce qui nous permet d’atteindre une haute efficacité énergétique et de nombreuses fonctionnalités différentes dans des dispositifs très petits. Nous avons une bonne architecture de dispositif et un bon matériau avec lesquels travailler, mais nous devons continuer à innover pour découvrir les limites ultimes de performance », conclut Shao.

Source : MIT